物理气相沉积(PVD)介绍

发布时间:2017-04-01

虽在IC晶片制造程序上,必然会使用到各种不同种类的导体,而低电阻的金属就常使用在微电子电路的电子讯号连结上。而各类金属薄膜制作过程,也就成为电子电路必备的制作程序之一。物理气相沉积(Physical Vapor Deposition)是以物理机制来进行薄膜沉积技术,所谓物理机制就是物质的相变化,如蒸镀(Evaporation)、溅镀(Sputtering)。而这种过程无涉及化学反应,因此所沉积的材料纯度佳且品质稳定。而PVD的溅镀制作过程,可以达成快速的沉积速率、准确的沉积厚度控制、精确的成份控制及较低的制造成本。所以溅镀是目前半导体工业所大量采用的薄膜制作方式,以目前之金属化制作过程来看:Ti、Ta、TiN、TaN等所谓的反扩散层或是黏合层及导线连接Al/Cu,都可使用物理气相沉积法来完成。本文将浅略的介绍PVD的种类、原理、先天的缺陷以及克服缺陷的方式,让阅读者对PVD有初步的认识。

PVD的种类与原理

1.1、蒸镀(Evaporation)

蒸镀原理(图1、图2)是在高真空腔体中,放入所要蒸镀的材料,利用电热丝或电子束加热升温达到熔化、气化温度,使材料蒸发,到达并附着在基板(晶圆)表面上的一种镀膜技术。在蒸镀过程中,被镀物的表面温度对蒸镀所形成的薄膜的特性有很重要的影响。基板须要适当加热,使得蒸镀原子可以在基板表面自由移动,如此才能形成均匀的薄膜。基板加热至150℃以上时,可以使沉积膜与基板间形成良好的键结而不致剥落。

1.2、溅镀(Sputter)

Sputter是利用在高真空的环境下,反应室通入适当的气体(大多使用氩气Ar),并控制在适当的压力下,反应室内的自由电子去撞击Ar分子,造成Ar的解离,产生二次电子与Ar离子,Ar离子受到靶材上负电位的影响,加速去撞击靶材,将靶材上的金属给撞击下来,并沉积在晶片表面上。(图3)靶材的冷却则是当靶材不断受到高能量(温度与速度)的Ar离子轰击,会使得靶材的温度持续升高,温度过高将破坏靶材与周边治具的结合,因此必须冷却。一般靶材都是用水冷却,冷却水流过靶材背面将热量带走,达到冷却的目的。

绝缘材料的溅镀乃绝缘薄膜须利用射频溅镀或反应溅镀。若采用直流电溅镀,将造成靶材表面电荷持续堆积而无法溅镀。电荷持续堆积过量,可能瞬间放电,产生高能高热,损坏靶材与周边。例如TiO2、Ta2O3⋯等。所谓反应溅镀(Reactive Spuutering)是溅镀时将反应性气体加入腔体中进行反应。例如:在氩气加氮气的环境下溅镀钛,会形成氮化钛(TiN)。

PVD镀膜技术特殊效应与现象

Sputter其主要镀膜优点是纯度高、低温可形成薄膜,而其最大的缺点就是阶梯覆盖率(Step Coverage)比较差(相较于CVD)。溅镀本身受到溅射原子多方向与多角度散射的影响下,不易在非水平表面下,得到连续且均匀覆盖(Conformal)的薄膜。当制作过程线宽极小化的时后,用传统PVD镀膜的方式就有其缺陷存在。图4为阶梯覆盖率不良的示意图。

阶梯覆盖率改善的方式

2.1、基板加温:加热基材表面,使封口时机延后

2.2、使用准直管(图5)

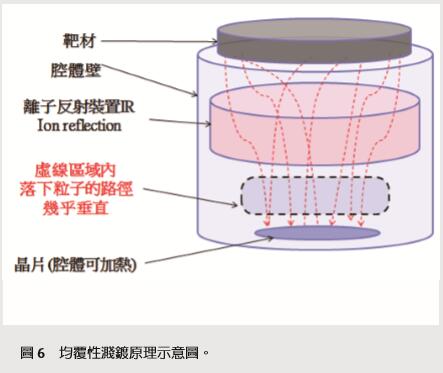

2.3、使用力场将粒子移动方向拉直(图6)

物理气相沉积(PVD)是目前在半导体制作过程中,最被广泛与常态运用于金属薄膜、金属氮化物、氧化物的镀膜技术。虽然在小线宽的薄膜沉积能力,化学气相沉积有较优的效果,即便如此PVD仍可透过各种不断创新的制作过程技术与设备去克服小线宽阶梯覆盖率不良的问题。因此物理气相沉积法仍在半导体制作过程上,依旧占有着举足轻重、不可或缺的关键性角色。目前各项薄膜技术中,PVD成膜速度及薄膜纯度等优点,仍是PVD最大的优势。相信在可预见的未来,半导体及相关电子产业界,物理气相沉积仍是不可能被取代。

声明:本站部分图片、文章来源于网络,版权归原作者所有,如有侵权,请点击这里联系本站删除。

| 返回列表 | 分享给朋友: |

- 上一篇:PVD镀制钛金属涂层的特性

- 下一篇:PVD涂层技术的使用为何能占半壁江山?看…

京公网安备 11010502053715号

京公网安备 11010502053715号